- Joined

- May 27, 2016

- Messages

- 3,477

This explains some of my thinking. My apologies, there is a lot here.

Op-Amps

I am back and getting technical amid all sorts of decisions in getting my circuit together. The critical op-amps used in the transimpedance front-end are decided, as are the ADC drivers. My ADC has differential input, and needs the interface to single ended operation.

Gain distribution and noise.

I opted to have the first TIA gain resistance not be 1M, nor any of the "higher" values I have seen in TIA circuits. Instead, it is at a value where it's noise contribution is below that of the amplifier input. There is not much point in having a amplifier capable of seeing down to the PIN diode noise floor, then throwing that advantage away with a spectacular, bandwidth-limiting TIA one-stage gain. Anything above about 36dB there puts the noise figure safe from any subsequent circuitry, and relaxes the noise specification for op-amps we might use.

Thus, after the first TIA stage follows one or two op-amps to get to the final gain, and correct signal polarity.

Hardware triggers removed

To keep things simple, and reduce components, I have opted to not include window comparator trigger, which would use up a dual IC. Triggers can be done better in software.

Hardware peak detect removed

Similarly, I have removed the peak-detect -> peak hold. I am sure it does a great job, but for the same reasons as trigger, having the sampled pulses captured means the peak is quite available in software, without quite tricky high bandwidth hardware, each with a price!

50Hz / 60Hz Notch Filter

This is something I do include in the design. It is easy enough to leave out, replaced by a link. There are a whole bunch of different types, from expensive "programmable" state-variable filters. Twin-T with 2 opamps, Fliege topology, Bainter Notch, etc.

The well-known Twin-T with the two-op-amps simulated using the same LT1807 as for the ADC driver giving a -48dB notch. Throwing in two sets of passives resistors and capacitors, aimed at making 50Hz and 60Hz notches all in one go removed a band from 49.5Hz to 61Hz to -56dB, with a hump at 55Hz at about -48dB. The notches themselves were at -64dB for 50Hz, and -72dB for 60Hz.

I don't know how this actually works! The dedicated single-frequency 60Hz hum remover by itself does not do as well. It simulates at -50dB.

We learn how much the actual performance of these much depends on tolerance and balancing of critical components, and how some circuits are much more tolerant. Simulated performance showing notches 70dB to 100dB deep are more likely to achieve 50dB to 60dB in practice.

I have found notch filters implemented with a couple of old-school bipolar transistors that seem to have spectacular performance!

OnefFilter package - regardless

I am much tempted by the Twin-T, regardless it has six passives that need to be really good. Some others are also tempting, but need three or four op-amps. Whichever we use, the filter takes one physical package, a dual, or a quad. It does not have to have a special low noise, but does need a gain-bandwidth product good enough to deliver 300kHz undistorted. That would mean 20MHz minimum. The LT1807's are there just because I have them around. For a 4-op-amp package, I thought maybe ADA4891-4ARUZ-R7. It's not pennies at £3.56 for one IC with 4 opamps in it.

If anyone has a suggestion for your favourite affordable op-amps in dual or quad small-outline SMD that are up to delivering deep notch filters while still having acceptable gain of at least x1 over the bandwidth we need for the rest of the pulse signal, then here is the place to say what is your favourite. Pin-outs for 14 and 16-pin packs tend to be standard. It may be one can throw in whatever is to hand at the time.

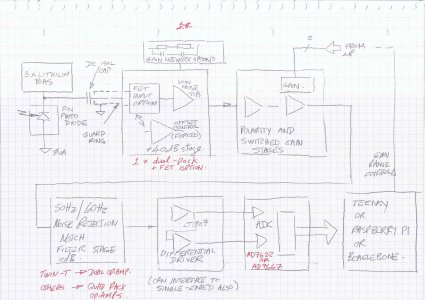

The sketch

I include here a scrappy little sketch which may help @rwm to imagine what's there. I left a lot out, like the special lengths we go to regulated supplies, and prevent overloading anything. Sorry, but right now is not when I want to be producing drawing package documentation.

The (simple) arrangement

Start with the PIN diode, which has 3 x lithium button cells for bias, fed through a high value current limiting resistor with it's noise shunted by capacitor. I drew a lot from the TIA circuits of Glen Brisebois (Linear Technology) contributions from 2001 through 2022. Going back to the two basic ways we operate these PIN diodes, most circuits seen operate in photovoltaic mode at zero bias, and not at X-ray wavelengths. Photons arrive, and make volts, just like the solar panel on your roof!

We, instead, bias the large area diode OFF with 10V, and so we create a depleted layer that won't conduct, and it has a much reduced capacitance for it's (huge) area. Photons arrive in that insulating layer, and make electrons that will get gathered up by the bias field, and so we get a pulse.

The DC isolation capacitor

This would normally be a thing that loses us control of where the "bottom" of the pulse is. No more DC reference! In theory, the signal should float to where the pulse average is - except this one does not! The capacitor is optimum, fully big enough to deliver all the energy in the capacitance of the PIN diode in one quick pulse, without affecting it's amplitude. In simulation, I did not see the base line drift up. Here we are dealing with between 80pA and about 5nA. It seemed to work! Losing the 10V bias lets us use the very low noise TIA front end circuits.

First stage gain choice

As explained before, and drawing my earlier times having to fish a clean signal from some feeble satellite, the gain has to be enough to ensure that only the signal, and the noise of molecules banging about in the first stage are what gets amplified. If enough gain, the noise will be so huge as to make any subsequent stages noise contributions become trivial. Of course, the signal got amplified as well. The S/N signal/noise ratio is preserved. To this end, the TIA gain resistor is chosen not be be so large as to mess it up.

A 1Meg resistor is 130nV/√Hz, and if we want 300KHz bandwidth to nicely preserve the wave-shape of a 13uS pulse, then it makes 71uV, which is a darn racket compared to the 4.3nV/√Hz input of out op-amp, making only 2.3uV. I will be experimenting with that resistor, going for a value some 10's of K, and possibly using one of the feedback TIA networks explained by Jerald Graeme, and used by Hammamatsu Corp.

There is also the option of the FET input, also from Brisebois.

What's with the extra FET?

This is an optional variation to the TIA circuit. The FET and one op-amp work together, with the other op-amp in the pack used to force the bias at the FET to be zero. This can also be done without the FET.

So what is there?

In practice, this first stage is a LTC6268, which is a single lonely op-amp in a 8-pin SO pqackage. This is to have enough spacing between the input pins to allow a guard ring track. At it's simplest option, that is the only amplifier there. The feedback resistor is put in as two in series, to limit the stray capacitance across, and the stability compensation (a few pF) is contrived by having two SMD capacitors in series.

There is some minor tracking to allow using any of the "Feedback Tee" circuits from the traditional wisdom TIA book. These are just tracking options, not having components on unless you want to play.

If a FET input stage is chosen (simulated so far as best), then one has to drag in another op-amp, which needs to be low noise, but not necessarily as wideband as the LTC6268. There are a few resistors and capacitors that go with these active parts.

The rest of the gain

In my circuit, this is provided by two stages. They might be the op-amps in just one package. The input noise requirement is no longer there, but they need to be fast enough, and work within the 2.5V. First is a necessary polarity reversal, plus a huge chunk of gain. The next part has logic switched analogue gain range settings controlled from the little computer. This gain feature need not be there. Just ignore it and settle for one resistor if you like, or leave out the whole op-amp, although it will still be there in the package. Analogue switches can be ADG1201BRJZ or LTC202CS#PBF. The first is SPDT -NO (single pole double throw - normally open) or the latter is Quad SPST (single pole single throw). I have not tried it yet.

The 60Hz interference noise rejection filter

This is explained elsewhere earlier in this post. I see it as something we should have. I am just not sure where it should go. Should it be where I have shown it, or should it be immediately after the TIA? I will take suggestions on this point.

The ADC driver.

Most ADCs need a good driver, and this one takes it's supply from the ADC chip itself. If one has a ready-made single ended signal, and an ADC that does not care, then just leave it out. Alternatively, it can drive both the ADCs @homebrewed and I have been discussing. At this point, I was implementing from the circuits shown in the datasheet.

The KiCad circuit

This is still evolving. It seems everything I want is often just not available, or if taken from a supply site, comes locked up with all sorts of other software marketing lock-in tools. I have to "edit" the models to get what I want, without their add-ons. I end up making a lot of my own symbols. When I have it, and am getting down to tracking, I will post it. Folk here may have a opinion on whether we should exchange complete stuff via PM. If I have any PCBs over, even partially assembled, I am OK to distribute them between us.

Op-Amps

I am back and getting technical amid all sorts of decisions in getting my circuit together. The critical op-amps used in the transimpedance front-end are decided, as are the ADC drivers. My ADC has differential input, and needs the interface to single ended operation.

Gain distribution and noise.

I opted to have the first TIA gain resistance not be 1M, nor any of the "higher" values I have seen in TIA circuits. Instead, it is at a value where it's noise contribution is below that of the amplifier input. There is not much point in having a amplifier capable of seeing down to the PIN diode noise floor, then throwing that advantage away with a spectacular, bandwidth-limiting TIA one-stage gain. Anything above about 36dB there puts the noise figure safe from any subsequent circuitry, and relaxes the noise specification for op-amps we might use.

Thus, after the first TIA stage follows one or two op-amps to get to the final gain, and correct signal polarity.

Hardware triggers removed

To keep things simple, and reduce components, I have opted to not include window comparator trigger, which would use up a dual IC. Triggers can be done better in software.

Hardware peak detect removed

Similarly, I have removed the peak-detect -> peak hold. I am sure it does a great job, but for the same reasons as trigger, having the sampled pulses captured means the peak is quite available in software, without quite tricky high bandwidth hardware, each with a price!

50Hz / 60Hz Notch Filter

This is something I do include in the design. It is easy enough to leave out, replaced by a link. There are a whole bunch of different types, from expensive "programmable" state-variable filters. Twin-T with 2 opamps, Fliege topology, Bainter Notch, etc.

The well-known Twin-T with the two-op-amps simulated using the same LT1807 as for the ADC driver giving a -48dB notch. Throwing in two sets of passives resistors and capacitors, aimed at making 50Hz and 60Hz notches all in one go removed a band from 49.5Hz to 61Hz to -56dB, with a hump at 55Hz at about -48dB. The notches themselves were at -64dB for 50Hz, and -72dB for 60Hz.

I don't know how this actually works! The dedicated single-frequency 60Hz hum remover by itself does not do as well. It simulates at -50dB.

We learn how much the actual performance of these much depends on tolerance and balancing of critical components, and how some circuits are much more tolerant. Simulated performance showing notches 70dB to 100dB deep are more likely to achieve 50dB to 60dB in practice.

I have found notch filters implemented with a couple of old-school bipolar transistors that seem to have spectacular performance!

OnefFilter package - regardless

I am much tempted by the Twin-T, regardless it has six passives that need to be really good. Some others are also tempting, but need three or four op-amps. Whichever we use, the filter takes one physical package, a dual, or a quad. It does not have to have a special low noise, but does need a gain-bandwidth product good enough to deliver 300kHz undistorted. That would mean 20MHz minimum. The LT1807's are there just because I have them around. For a 4-op-amp package, I thought maybe ADA4891-4ARUZ-R7. It's not pennies at £3.56 for one IC with 4 opamps in it.

If anyone has a suggestion for your favourite affordable op-amps in dual or quad small-outline SMD that are up to delivering deep notch filters while still having acceptable gain of at least x1 over the bandwidth we need for the rest of the pulse signal, then here is the place to say what is your favourite. Pin-outs for 14 and 16-pin packs tend to be standard. It may be one can throw in whatever is to hand at the time.

The sketch

I include here a scrappy little sketch which may help @rwm to imagine what's there. I left a lot out, like the special lengths we go to regulated supplies, and prevent overloading anything. Sorry, but right now is not when I want to be producing drawing package documentation.

The (simple) arrangement

Start with the PIN diode, which has 3 x lithium button cells for bias, fed through a high value current limiting resistor with it's noise shunted by capacitor. I drew a lot from the TIA circuits of Glen Brisebois (Linear Technology) contributions from 2001 through 2022. Going back to the two basic ways we operate these PIN diodes, most circuits seen operate in photovoltaic mode at zero bias, and not at X-ray wavelengths. Photons arrive, and make volts, just like the solar panel on your roof!

We, instead, bias the large area diode OFF with 10V, and so we create a depleted layer that won't conduct, and it has a much reduced capacitance for it's (huge) area. Photons arrive in that insulating layer, and make electrons that will get gathered up by the bias field, and so we get a pulse.

The DC isolation capacitor

This would normally be a thing that loses us control of where the "bottom" of the pulse is. No more DC reference! In theory, the signal should float to where the pulse average is - except this one does not! The capacitor is optimum, fully big enough to deliver all the energy in the capacitance of the PIN diode in one quick pulse, without affecting it's amplitude. In simulation, I did not see the base line drift up. Here we are dealing with between 80pA and about 5nA. It seemed to work! Losing the 10V bias lets us use the very low noise TIA front end circuits.

First stage gain choice

As explained before, and drawing my earlier times having to fish a clean signal from some feeble satellite, the gain has to be enough to ensure that only the signal, and the noise of molecules banging about in the first stage are what gets amplified. If enough gain, the noise will be so huge as to make any subsequent stages noise contributions become trivial. Of course, the signal got amplified as well. The S/N signal/noise ratio is preserved. To this end, the TIA gain resistor is chosen not be be so large as to mess it up.

A 1Meg resistor is 130nV/√Hz, and if we want 300KHz bandwidth to nicely preserve the wave-shape of a 13uS pulse, then it makes 71uV, which is a darn racket compared to the 4.3nV/√Hz input of out op-amp, making only 2.3uV. I will be experimenting with that resistor, going for a value some 10's of K, and possibly using one of the feedback TIA networks explained by Jerald Graeme, and used by Hammamatsu Corp.

There is also the option of the FET input, also from Brisebois.

What's with the extra FET?

This is an optional variation to the TIA circuit. The FET and one op-amp work together, with the other op-amp in the pack used to force the bias at the FET to be zero. This can also be done without the FET.

So what is there?

In practice, this first stage is a LTC6268, which is a single lonely op-amp in a 8-pin SO pqackage. This is to have enough spacing between the input pins to allow a guard ring track. At it's simplest option, that is the only amplifier there. The feedback resistor is put in as two in series, to limit the stray capacitance across, and the stability compensation (a few pF) is contrived by having two SMD capacitors in series.

There is some minor tracking to allow using any of the "Feedback Tee" circuits from the traditional wisdom TIA book. These are just tracking options, not having components on unless you want to play.

If a FET input stage is chosen (simulated so far as best), then one has to drag in another op-amp, which needs to be low noise, but not necessarily as wideband as the LTC6268. There are a few resistors and capacitors that go with these active parts.

The rest of the gain

In my circuit, this is provided by two stages. They might be the op-amps in just one package. The input noise requirement is no longer there, but they need to be fast enough, and work within the 2.5V. First is a necessary polarity reversal, plus a huge chunk of gain. The next part has logic switched analogue gain range settings controlled from the little computer. This gain feature need not be there. Just ignore it and settle for one resistor if you like, or leave out the whole op-amp, although it will still be there in the package. Analogue switches can be ADG1201BRJZ or LTC202CS#PBF. The first is SPDT -NO (single pole double throw - normally open) or the latter is Quad SPST (single pole single throw). I have not tried it yet.

The 60Hz interference noise rejection filter

This is explained elsewhere earlier in this post. I see it as something we should have. I am just not sure where it should go. Should it be where I have shown it, or should it be immediately after the TIA? I will take suggestions on this point.

The ADC driver.

Most ADCs need a good driver, and this one takes it's supply from the ADC chip itself. If one has a ready-made single ended signal, and an ADC that does not care, then just leave it out. Alternatively, it can drive both the ADCs @homebrewed and I have been discussing. At this point, I was implementing from the circuits shown in the datasheet.

The KiCad circuit

This is still evolving. It seems everything I want is often just not available, or if taken from a supply site, comes locked up with all sorts of other software marketing lock-in tools. I have to "edit" the models to get what I want, without their add-ons. I end up making a lot of my own symbols. When I have it, and am getting down to tracking, I will post it. Folk here may have a opinion on whether we should exchange complete stuff via PM. If I have any PCBs over, even partially assembled, I am OK to distribute them between us.

Attachments

Last edited: